A ideia deste trabalho não é a de apresentar a descrição de uma montagem em si, mas sim a de expor elementos para que o leitor possa montar a campainha musical proposta a partir, é claro, dos circuitos básicos que serão mostrados no decorrer desta publicação.

Tais circuitos básicos, a bem da verdade, podem ser considerados como blocos que, convenientemente interligados, oferecem resultados mais do que satisfatórios.

Esses blocos, em quantidade de quatro, são os seguintes:

— Bloco "musical";

— Bloco "temporizador";

— Bloco "amplificador" e

— Bloco "fonte de alimentação".

Cada um deles funciona, praticamente, de forma independente dos demais; desta forma o leitor poderá utilizar apenas o bloco "musical" ou este associado ao bloco "amplificador" ou, em caso extremo, ambos blocos quando, então, obterá um verdadeiro sistema musical (desculpem o mau jeito!) de até oito notas que serão repetidas sequencialmente durante um "pedaço" de tempo estabelecido pelo conjunto de temporização e, o que é mais importante, com volume suficiente para deixar qualquer um "maluquinho da silva"!

Quanto ao consumo do aparelho... "pura bobagem": uns "pouquinhos" miliampères se em repouso e da ordem de 250 quando em máximo volume, isto ao serem utilizados os quatro blocos constituintes do sistema!

BLOCO "MUSICAL"

Este bloco é formado por quatro CI's (circuitos integrados), dois dos quais são do mesmo tipo, exatamente o conhecidíssimo C.I.555, que já tem sido tema de várias publicações e de livros, um dos quais é de minha autoria (um pouco de propaganda não faz mal a ninguém, mesmo com a "Lei Falcão" imposta pela Redação da Revista!).

O C.I. 555 normalmente se apresenta na conhecida mecânica, tipo "dil" (duplo em linha) de 4 + 4 pinos; além do invólucro plástico, o C.I. também se apresenta sob um invólucro metálico, por sinal pouco difundido.

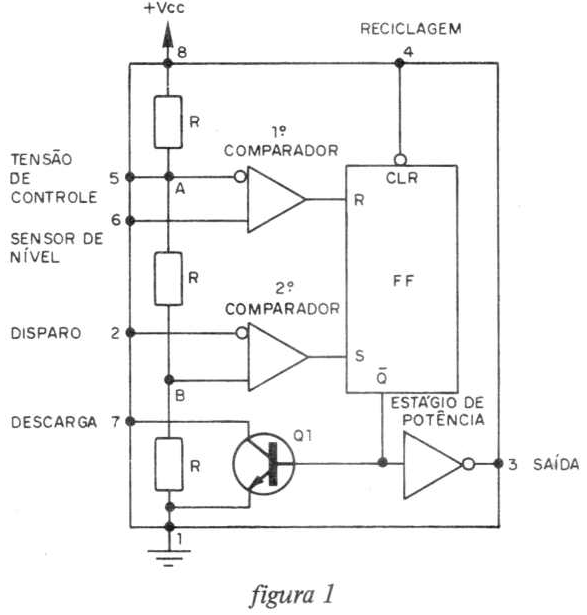

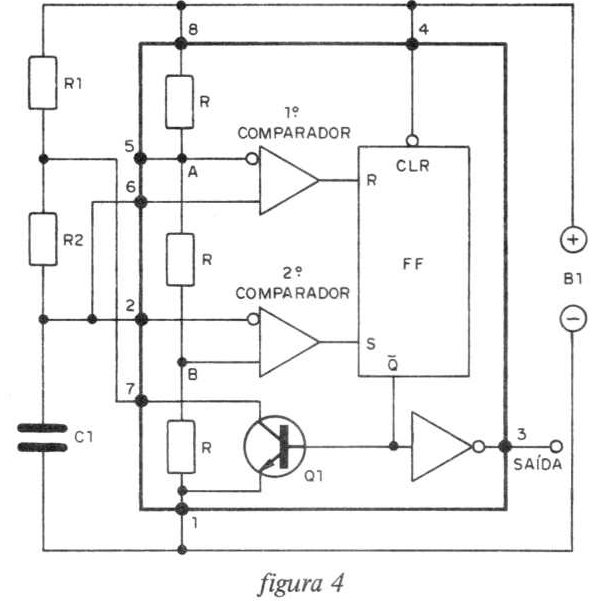

O circuito interno deste C.I. é basicamente formado por três resistências do mesmo valor ôhmico, dois comparadores de tensão, um flip-flop (biestável) e um transistor "adicional" que é comandado através de base pela saída Q do biestável. Na figura 1 é mostrada a estrutura interna básica do integrado, bem como a identificação dos pontos de acesso.

Essas três resistências R, veja a figura 1, estabelecem os seguintes potenciais para os nós A e B: 2/3 de Vcc e 1/3 de Vcc respectivamente, tornando-se a referência para cada um dos comparadores de tensão. A entrada do primeiro desses comparadores (pino 6) sensibiliza-o quando o potencial do sinal aplicado é superior a 2/3 de Vcc, enquanto o segundo é sensibilizado por sinais de amplitude inferior a 1/3 de Vcc aplicados à sua entrada "disparo" (pino 2).

A saída de cada um desses comparadores "ataca" o flip-flop (abreviadamente FF): o primeiro através da entrada reciclagem (R) e o segundo através da entrada sensibilização (S). A comutação do FF é, portanto, controlada através de potenciais aplicados aos pinos 2 e 6 do C.I., a menos que a entrada de reciclagem (pino 4) se encontre aterrada quando, então, o FF permanecerá no estado de repouso, independentemente dos demais comandos — o leitor já percebeu que esta entrada tem prioridade sobre as demais (no projeto em questão não foi prevista a sua utilização assim como a da entrada "tensão de controle", cuja função básica é a de estabelecer, através de componentes externos, os níveis de disparo dos comparadores do C.I.).

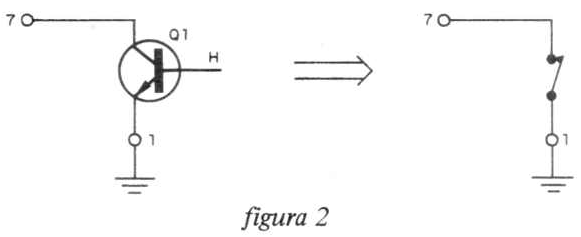

Supondo o FF em repouso, isto é, reciclado, teremos a saída Õ em nível alto, "forçando" a circulação de corrente através da base do transistor Q1 que, por ser do tipo NPN, satura e, assim, o pino 7 do C.I. é levado ao potencial terra (veja na figura 2 a analogia entre a saturação de Q1 e a operação de um interruptor mecânico convencional); por outro lado, esse mesmo potencial alto de Q complementado pelo amplificador de potência, surgindo na saída do C.I. (pino 3) um "terra", ou seja, um potencial baixo, ou nulo se quiserem.

Uma vez que o FF está reciclado de nada resolverá elevar o potencial na entrada "sensor de nível", pois o comando de saída do primeiro comparador será ignorado pelo FF. É claro! Se o FF se encontra, por hipótese, reciclado as informações de reciclagem serão ignoradas, temos, isso sim, que sensibilizar o biestável caso queiramos a comutação do nível lógico de saída.

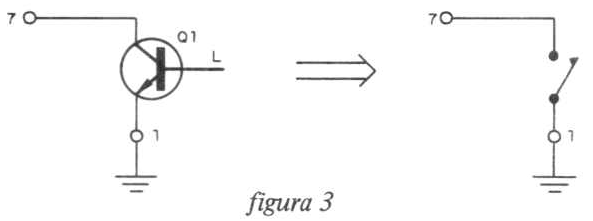

A sensibilização é conseguida se a "gente" levar o potencial da entrada "disparo" a um valor menor que 1/3 de Vcc, aí sim, o segundo comparador de tensão "ataca" o FF que se vê obrigado a "virar", em consequência temos Q em nível baixo (aproximadamente zero volts) que retirará da saturação Q1 ao mesmo tempo que o amplificador de potência se encarregará de expor um nível alto (aprox. Vcc) na saída do 555 — para você que ainda está um pouco "cru" em eletrônica, veja a figura 3 onde é feita uma analogia entre o corte de Q1 e um interruptor convencional.

Um ponto curioso para observar é o fato do 555 manter-se ativo mesmo que a excitação anterior seja retirada da entrada "disparo", ou mesmo se outras excitações adequadas forem aplicadas a essa mesma entrada.

Para retornar o C.I. à condição inicial (repouso) é necessário aplicar à entrada "sensor de nível" (vide figura 1) um sinal cuja amplitude em tensão seja superior a 2/3 de Vcc: o segundo comparador reciclará o FF e, em consequência, ter-se-á Õ em H (nível alto), forçando o nível L (baixo) na saída do 555 ao mesmo tempo que o transistor passará ao estado de forte condução (saturação) e.... eis que voltamos ao ponto de partida!

Antes que o leitor me venha com "lero-leros", em vez do procedimento acima poderíamos levar o pino 4 ao potencial terra (zero volts, por hipótese) com resultados semelhantes, mas esta função não foi utilizada no projeto.

As duas configurações básicas de funcionamento do C.I. 555 são como multivibrador astável e corno multivibrador monoestável — apenas a primeira será a analisada neste bloco.

No funcionamento como astável o 555 produz um trem de pulsos, cujo ciclo ativo/repouso é fixado por uma rede RC (resistor-capacitor) externa ao integrado — ao variar os valores dessa rede iremos variar a razão ciclo ativo/ciclo repouso, e, consequentemente, a frequência das oscilações.

O circuito da figura 4 dá uma ideia das interligações necessárias para o que o C.I. 555 opere como um astável. Aliás, o funcionamento como astável é caracterizado pela conexão dos terminais "sensor de nível" (pino 6) e "disparo" (pino 2) do circuito integrado.

Para efeito de raciocínio iremos supor que a fonte de alimentação B1 do circuito da figura 4 seja de 12 volts. Os potenciais dos nós A e B serão, então, respectivamente de 8 e 4 volts, já que os resistores R internos ao C.I. são do mesmo valor.

Vamos supor que o capacitor C1, figura 4, esteja carregado a um potencial inferior a 1/3 de B1, isto é, inferior a 4V no caso. Que acontecerá?

"Tá na cara" que o segundo comparador detecta essa tensão para menos e sensibiliza o FF e assim temos a saída em estado lógico alto (aproximadamente B1) enquanto Q1 se encarrega de retirar o aterramento do pino 7 do C.I. devido ao estado de corte em que se encontra provocado pela saída Q, no estado baixo, do FF.

Que o capacitor C1 está carregando-se isso é verdade! E o faz por intermédio das resistências R1, R2 e, é claro, pela energia fornecida pela fonte de alimentação B1.

Ao cabo de um momento as armaduras do capacitor alcançarão uma ddp (diferença de potencial) superior a 2/3 de B1 (no caso, 2/3 de 12V ou... 8V) e aí caberá ao primeiro comparador detectar essa tensão, para "mais", aplicada em sua entrada não inversora (pino 6); desta forma o FF recicla e a saída do C.I. passa para o nível baixo, ao mesmo tempo o transistor satura, aterrando o terminal 7 do integrado e assim o capacitor não mais poderá carregar-se através de R1 e R2, já que a corrente circulante por R1 será desviada, através de Q1, para o "—" da fonte de alimentação; também será desviada para terra a energia armazenada em C1 tão mais lentamente quanto maior for o valor de R2.

Chegará o momento em que a ddp sobre as armaduras do capacitor se torna inferior a 4 volts (1/3 de 61) e agora será a vez do segundo comparador surtir esse potencial inferior a 1/3 de B1, indo sensibilizar o FF como da primeira vez, dando início a novo ciclo, aliás a um novo semiciclo que culminará com a carga parcial de C1 (figura 4) até 2/3 de B1 quando, então, voltará a descarregar-se e.... assim por diante, dando continuidade às oscilações.

O leitor, assim como eu, já deve ter percebido que a ddp sobre C1 parte de aproximadamente 1/3 de B1, alcançando o valor de 2/3 de B1 para depois retornar ao limite inferior, gerando assim em forma de onda constituída por dupla exponencial: uma crescente (carga do capacitor) e outra decrescente (descarga de C1) mais pronunciada que a anterior, isto é, de menor duração — note que ele se carrega através de R1 e R2 enquanto sua descarga se efetua unicamente através de R2.

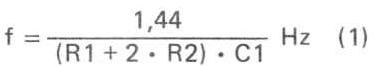

Um pouco de matemática e mais uns "ingredientes de raciocínio" nos levam à expressão abaixo, a qual permite estabelecer, em função de R1, R2 e C1, o valor da frequência TEÓRICA do trem de pulsos retangulares que esperamos obter na saída (pino 3) do C.I.:

onde R1 e R2 devem ser expressos em megohms (M ohms) e C1 em mIcrofarads (µF).

Se a "gente" no lugar de R1, figura 4, tiver uma resistência variável poderemos variar, a nosso gosto, o valor da frequência das oscilações. A mesma consideração também é válida para R2 e/ou C1.

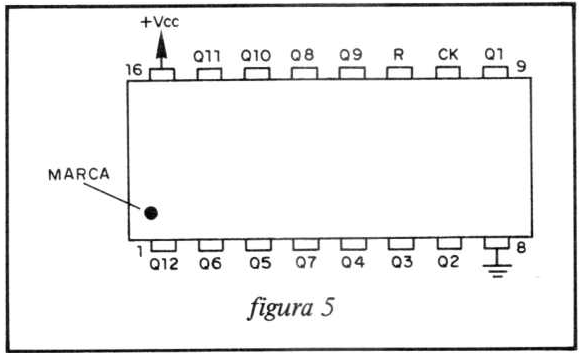

O outro integrado utilizado neste bloco é o contador binário 4040 de tecnologia CMOS que, assim como o 555, admite qualquer valor de tensão de alimentação compreendido entre 5Vcc até 17Vcc. Este C.I. é formado por flip-flops (ou estágios) cuja saída de cada um desses estágios é disponível pelo usuário; além dessas 12 saídas, identificadas por Q1 (menos significativa) até Q12 (saída mais significativa) o C.I. apresenta um par de entradas: a cadenciadora (CK) onde serão aplicados os pulsos a serem contados (sob a forma binária) e a entrada de reciclagem (R) que na presença do estado lógico "1" (estado H ou alto) situa todas as saídas no estado lógico "0", isto é, contagem nula.

A alimentação do C.I. é realizada através dos pinos 16 e 8, respectivamente + Vcc e terra, conforme vemos na figura 5 onde estão identificados os terminais do integrado em análise.

A entrada cadenciadora CK é sensível à borda posterior (flanco descendente) dos pulsos a ela aplicados, ou seja, o contador é incrementado quando "acabar" o pulso desde que, é claro, a entrada R se situe no estado lógico "0" — em caso contrário os pulsos em CK serão ignorados pelo contador, pois as 12 saídas "teimarão" em ficar no nível baixo ("0").

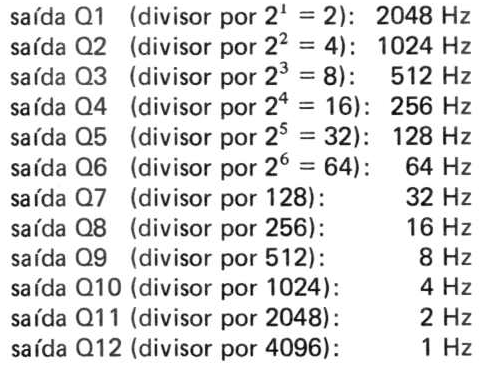

Ao aplicar na entrada CK um sinal de frequência, digamos, igual a 4096 Hz teremos os seguintes valores de frequência em cada uma das 12 saídas do 4040:

Daí percebemos que o índice i associado a cada saída Qi do C.I. representa a potência de 2 do quociente da divisão proporcionada naquela saída. O diagrama em fases da figura 6 mostra o comportamento das saídas para o caso de 30 pulsos de entrada: note como a frequência dos sinais de saída para saída, vai sendo reduzida à metade em relação à anterior. Observe também que ao encerrar-se um pulso de entrada temos nas saídas Q1 a Q12 uma série de valores lógicos que caracterizam um número binário, ficando assim caracterizada a contagem