Um analisador lógico faz duas coisas: registra o estado de alguns sinais digitais em uma memória durante algum tempo e, depois, mostra esses sinais em algum tipo de display para que o usuário veja quando cada mudança de estado aconteceu.

Augusto Einsfeldt

Nota: Artigo da Revista Saber Eletrônica 465 de outubro de 2012.

A correlação entre as mudanças de estado de cada sinal permite saber como um circuito digital está se comportando e, assim, é feita a análise do funcionamento. Para entender bem a importância de um analisador deste tipo imagine o seguinte exemplo de problema, que facilmente pode ocorrer durante o desenvolvimento de um projeto.

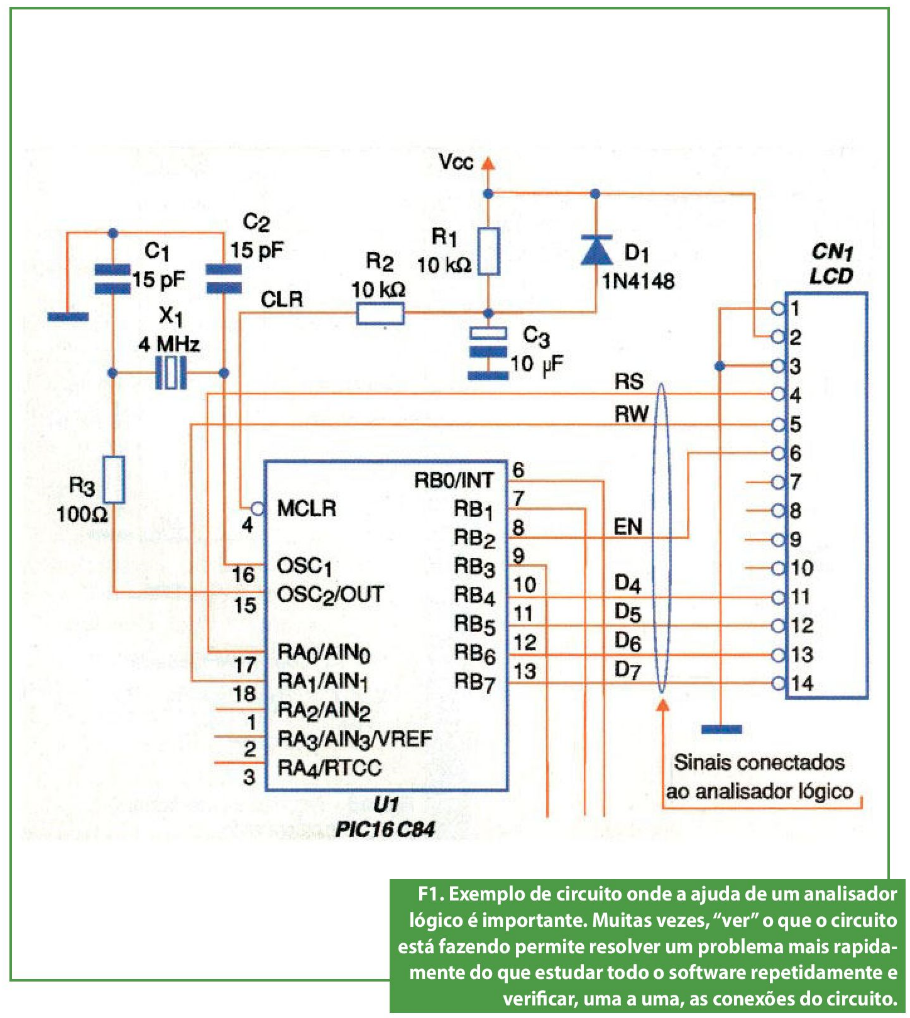

Em um determinado projeto, um microcontrolador está sendo usado para acionar um display LCD usando apenas os 4 bits mais significativos do barramento de dados (figura 1) e por mais que o software seja revisado, não se encontra o motivo para o display não estar funcionando.

Sabe-se que os displays LCD inteligentes (que possuem um processador incorporado) precisam receber um sequência de comandos muito específicos, e numa ordem precisa para serem inicializados corretamente. Isso é ainda mais complicado quando se usa apenas 4 bits dos 8 disponíveis no barramento de dados. Para saber o que está errado é preciso ter certeza que os dados estão chegando na ordem certa e alinhados segundo os demais sinais de controle (habilitação e endereço de escrita/leitura).

Procedimento: conectar os sinais de entrada do analisador lógico aos sinais a serem capturados (D4 a D7, EN, WR e RS), ajustar o analisador para adquirir dados após a primeira ocorrência do sinal EN, ligar o circuito mantendo o sinal de reset do microcontrolador (MCLR) ativo, armar o analisador (deixá-lo pronto para a aquisição dos dados, esperando pelo sinal de disparo) e, finalmente, liberar o MCLR para deixar o programa rodar. Depois, é só aguardar a captura do sinal e analisar os dados obtidos.

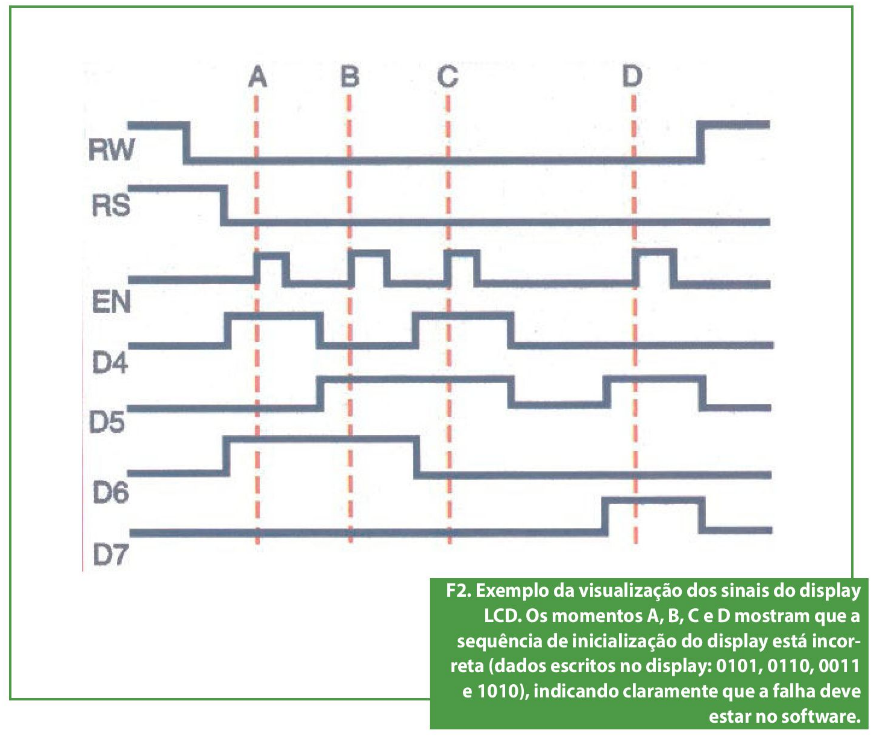

Na figura 2 é mostrado um diagrama de tempos dos sinais do exemplo acima. O display não funciona porque a sequência de inicialização está errada. Os primeiros 3 nibbles (palavra de 4 bits) escritos no display nos momentos A, B e C estão sendo 0101, 0110 e 0011. Eles deveriam ser 0010, 0010 e 1000. O tempo extra entre o terceiro nibble e os próximos dados está correto (notar a distância maior entre os momentos C e D). Entretanto, após o terceiro nibble, o display passa a aceitar dois nibbles consecutivos para montar cada byte de comando ou dados a serem enviados pelo microcontrolador. Assim, o sinal RW não poderia ter voltado ao nível 1 logo após o momento D e, sim, apenas após mais uma escrita de nibble, que seria um momento E não visualizado no diagrama dessa figura.

Toda esta análise indica que o software está cometendo alguns erros bem específicos e, por isso, é razoavelmente fácil a tarefa de encontrar as falhas no programa. Sem o analisador lógico, o projetista poderia demorar muito mais para encontrar o motivo da falha. Quem já programou um microcontrolador sabe que é muito comum examinar um trecho do software dezenas de vezes sem conseguir perceber onde está a falha. Nos programas que usam indexação para acessar tabelas ou uso intensivo de interrupções, a falha pode ser quase invisível se o projetista não tiver uma pista sobre o momento em que ela ocorre.

O projeto

O analisador lógico apresentado neste artigo é um projeto relativamente simples e econômico. Usando-o como ponto de partida o leitor poderá implementar outras funções e ampliar sua capacidade, conforme sua imaginação e recursos. Este modelo captura 8 sinais digitais em uma memória RAM estática de 32 kB e permite transferir os dados capturados por uma porta serial RS-232 a uma taxa de 38.400 bps. Um programa rodando em um computador faz a leitura destes dados e apresenta o diagrama de tempos em formato gráfico. Esta dependência de um computador para visualizar os dados poderia, por exemplo, ser resolvida por algum leitor experiente alterando o projeto e empregando um display gráfico LCD associado a um microcontrolador. Esta solução permitiria construir um analisador lógico no formato de equipamento único e independente.

A velocidade de captura depende da duração da máquina de estados interna necessária para temporizar os sinais de controle da memória. Neste projeto cada byte capturado precisa de aproximadamente 400 ns, ou seja, na velocidade máxima pode-se capturar 2,5 MB/s e os 32 kB são preenchidos em 13,1 milissegundos. Além disso, o projeto possui outras características:

• Palavra de trigger (disparo) selecionável entre 8, 4, 3 e 1 bits de largura.

• Quatro fontes de clock de captura (interno máximo (400 ns), externo, externo invertido e manual)

• Trigger manual, ou automático (usando a palavra de trigger)

• Parada manual, ou no término da memória.

• Trigger manual gerado por botão, ou sinal vindo da RS-232 (RTS)

• Descarga da memória via serial, velocidade 38.400 bps (cerca de 9 segundos)

• Baixo consumo de energia, permitindo montagem compacta e uso de pilhas

• Usa apenas três circuitos integrados (a RAM, um CPLD Xilinx CoolRunner XCR3064 XL e um 74HC14, com um custo em componentes menor de US$ 10).

Empregando CPLDs maiores, memórias mais rápidas e algumas alterações de projeto que dependem do modo de operação da memória RAM, pode-se aumentar a velocidade de aquisição para até 20 MB/s facilmente, assim como estender a capacidade de armazenamento para, por exemplo, 256.000 palavras de 16 bits.

Como funciona

O circuito do analisador lógico possui alguns sinais de entrada e saída (além da interconexão entre a memória SRAM e o CPLD):

• 8 sinais de entrada de dados para captura

• 1 entrada de sinal de clock externo

• 8 chaves para seleção de palavra de trigger automático

• 2 chaves para seleção da largura da palavra de trigger

• 1 chave para selecionar modo de trigger: Manual ou Automático

• 2 chaves para selecionar a fonte de clock

• 1 chave para selecionar o modo de operação: Captura ou Transmissão

• 1 botão de RESET

• 1 botão de disparo/interrupção MANUAL

• 1 LED de fim de operação

• 1 LED de "aguardando disparo"

• Interface serial (TXD, RXD, RTS, DTR e CTS).

• Os sinais "internos" ao circuito são:

• 15 bits de endereço para a RAM

• 8 bits de dados da RAM

• 3 sinais de controle da RAM (CS, WR, OE)

• 1 entrada de clock

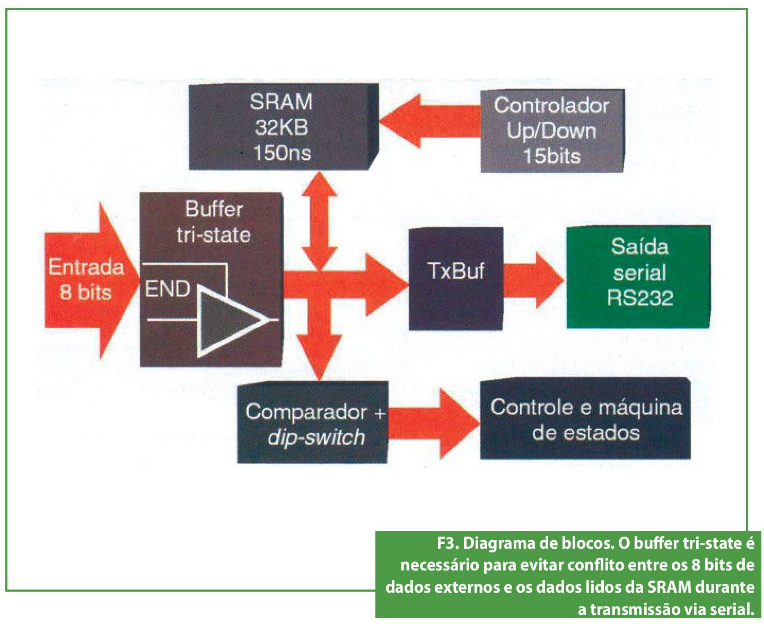

A figura 3 ilustra o diagrama de blocos do analisador lógico. O funcionamento básico é simples: no modo Captura, o circuito espera por um sinal de trigger (disparo) que pode ser detectado automaticamente através da comparação de um ou mais bits dos dados de entrada com o estado das chaves de seleção de trigger.

Outra forma de obter o trigger é por um sinal manual, que pode ser gerado pelo botão MANUAL ou através de um sinal vindo da porta serial (RTS). Após o trigger, o circuito inicia a captura dos dados na entrada e guarda-os sequencialmente na memória RAM estática. A captura é contínua e termina apenas ao chegar no fim da memória, ou caso o usuário pressione o botão MANUAL.

O ritmo de captura dos dados é ditado pela fonte de clock. Cada vez que este sinal está ativo, uma máquina de estados é acionada para gerar os sinais de controle de escrita da RAM. Esta máquina possui apenas 3 estados e emprega o clock de referência de 10 MHz. Isso quer dizer que a manipulação dos sinais da memória RAM demora 300 ns (três ciclos de clock de 10 MHz). Durante uma captura contínua e empregando o clock interno, o circuito ainda precisa de mais um ciclo de clock para acertar alguns sinais internos. Assim, a velocidade máxima de aquisição de dados fica em 2,5 Msps (ou 400 ns de intervalo entre cada gravação na RAM estática).

Portanto, devido à máquina de estados o circuito vai reconhecer um novo clock de aquisição apenas no final do processo de escrita na memória. Se esse clock de aquisição ocorrer antes do final do processo, ele não será considerado, e se ele surgir muito depois do final do processo o circuito ficará esperando por ele sem fazer mais nada. Se o clock for manual, cada vez que o usuário pressionar o botão MANUAL a máquina de estados vai rodar e armazenar um byte na RAM. A mudança do modo de operação de Captura para Transmissão pode ser feita a qualquer momento, mesmo antes de terminar de preencher toda a memória.

No modo Transmissão, o circuito fica esperando que o usuário pressione o botão MANUAL para iniciar a leitura da RAM e enviar os dados pela porta serial. Os dados são enviados na ordem inversa da aquisição: primeiro será enviado o último byte capturado e depois os demais, decrescendo o endereçamento da memória, até chegar na posição zero. Embora esta ordem de transmissão pareça pouco natural, ela evita o consumo de mais recursos do CPLD. Claro que o software no lado do computador, que vai receber os dados via serial, deve permitir mostrar a ordem dos eventos no sentido correto.

Na transmissão usa-se uma máquina de estados para a serialização dos dados e um controle muito básico do acesso da memória. Em outras palavras, durante a leitura o sinal OE fica sempre habilitado e o sinal CS segue a operação do serializador da interface RS-232. O endereço da RAM é decrementado logo depois do dado no endereço atual, após ter sido memorizado em um registrador chamado TXBUF. Este registrador é usado para manter o dado estável enquanto é transmitido.

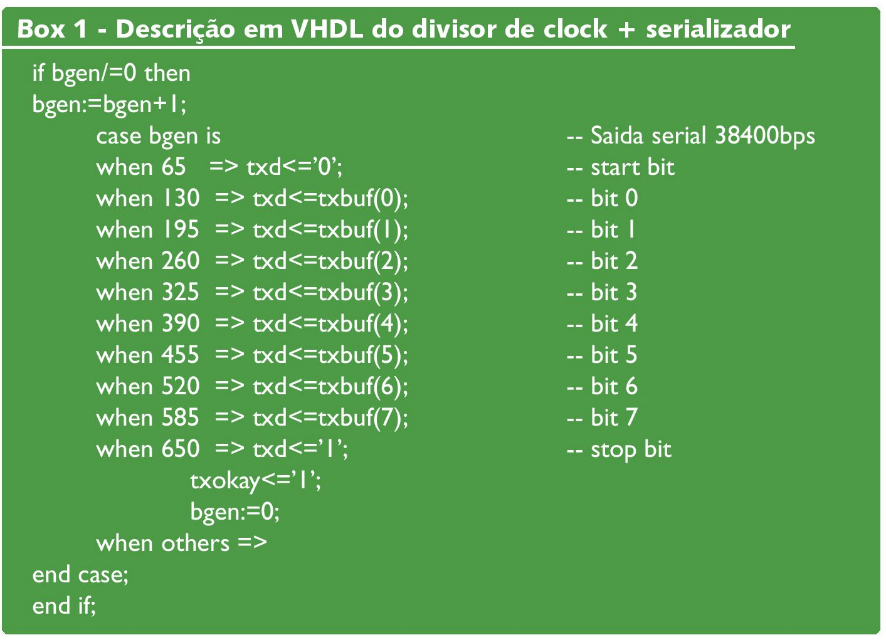

O processo de serialização neste projeto é um pouco diferente do convencional. Tipicamente, emprega-se um registrador de deslocamento (shift register) para converter dados paralelos em seriais, sendo que o clock deste shift-register é suprido por um divisor que ajusta o tempo de ciclo de acordo com a taxa de transmissão (baud rate) escolhida. Aqui emprega-se um único contador que faz a divisão do clock, e uma série de comparadores indicam em que ponto da contagem passou o intervalo de tempo de cada bit. Esta indicação faz o bit correspondente (armazenado em TXBUF ou os balizadores START e STOP) ser enviado para a interface serial.

Veja no box 1 a parte do projeto em VHDL mostrando o serializador.

Este analisador lógico foi ajustado para caber no CPLD XCR3064XL. O leitor poderá ampliar os recursos e facilidades ao empregar um CPLD maior (como o XCR3128XL, com 128 macro células). A intenção de usar um CPLD da família CoolRunner é tornar o circuito muito econômico em energia e permitir o uso de pilhas para sua alimentação. Isso dei a montagem final com tamanho bem reduzido, podendo ser um analisador lógico que cabe na palma da mão. Uma sugestão ao leitor que já tem boa experiência com eletrônica digital é incorporar um microcontrolador (como o MSP430) e um display LCD gráfico para obter um analisador lógico independente de computador. A descrição em VHDL possui cerca de 270 linhas e por ser grande assim não pode ser mostrada neste artigo. Contudo, você pode obtê-la acessando o web site: www.inix.com.br/srv_vhdl.asp.

Na segunda parte deste artigo será mostrado o circuito eletrônico e o programa de leitura que fica no PC.