O uso de processadores e lógica programável vem crescendo muito nos últimos anos. Para atender essa demanda crescente de aplicações, com restrições cada vez maiores na alimentação, estão surgindo conversores chaveados de alto desempenho e integração.

Gustavo Leão Moreira - Engenheiro de Aplicações na Macnica DHW -

Nota: Artigo publicado na Revista Saber Eletrônica 474 de novembro/dezembro de 2013.

Ao longo da última década, a porcentagem de projetos com FPGAs (Field Programmable Gate Arrays) e MCUs (Microcontrollers) deu um salto, passando de poucos milhões em 2003 a dezenas de milhões em 2013 no mercado nacional. Mercado que exige fontes mais limpas e baratas que performem elevada eficiência e garantam o bom funcionamento da parte digital.

Para atender essa demanda, houve a necessidade de criar uma nova arquitetura para a distribuição de potência na placa, denominada Point-of-Load (POL). Os POL fazem o trabalho árduo de converter uma tensão alta e pouco regulada do barramento de alimentação da PCI numa tensão de poucos volts, e precisa o bastante para ser utilizada pela lógica digital.

Uso de Point-Of-Load (POL)

O uso de POL vem para solucionar o problema da demanda de correntes elevadas e baixo ripple na tensão necessária para alimentar semicondutores mais modernos. Para isso, é adicionado um conversor (seja ele chaveado ou linear) próximo do seu ponto de uso e/ou carga. Neste artigo, o foco será o uso de POL chaveado, do tipo abaixador (buck). Normalmente, os POL funcionam com uma tensão de entrada de 12 VDC a 5 VDC e fornecem à carga tensões de 0,65 V a 3,3 V, com corrente na ordem de centenas de miliampères a uma centena de ampères,

No projeto de um POL, vários fatores devem ser levados em conta como a resistência de condução das chaves, retificação síncrona, tipo e valor dos capacitores de filtragem, modelo do indutor, resistência interna do indutor e capacitores, variação da capacitância com a tensão DC - principalmente quando o alvo é atingir baixo ripple de saída e alta eficiência na conversão. As etapas de seleção da frequência de chaveamento e ponto ótimo de trabalho também devem ser de domínio do projetista para obter-se um projeto de sucesso.

A vantagem em aumentar a frequência de chaveamento do POL

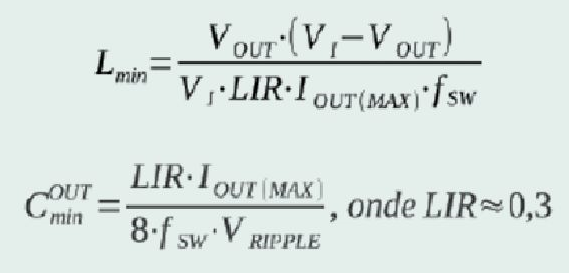

O conversar chaveado abaixador (buck) funciona através do armazenamento de energia da fonte no indutor - na forma de campo magnético - para posterior entrega dessa energia à carga. Esse processo de chaveamento entre armazenagem e entrega deve ser repetido periodicamente, para que o conversor opere de maneira satisfatória. Assim, a frequência de chaveamento (fsw) influencia na operação do circuito, con-forme pode ser visto na equações abaixo (variação da indutância com a frequência e variação da capacitância com a frequência):

Com o aumento da frequência, o indutor (normalmente o maior componente de uma fonte chaveada de pequena potência 0,5 ̴20 W) e os capacitores de entrada/ saída podem ser diminuídos, conforme pode ser visto pelas equações. A resposta transitória do circuito, com o aumento da frequência também é beneficiada, pois atinge mais rapidamente o valor de regime permanente, o ripple de entrada e saída da fonte são reduzidos e as perdas por ligar/desligar o canal do MOSFET também são menores. Ou seja, o projetista só tem a ganhar com o aumento da frequência!? Infelizmente não, o próximo tópico sobre perdas irá abordar o ponto negativo. Entretanto, mesmo havendo pontos negativos, as vantagens pesam mais que as desvantagens.

Ponto ótimo de operação do POL: perdas IR igual a perdas no chaveamento

O aumento da frequência de operação traz muitas vantagens para o funcionamento e diminuição dos componentes passivos do circuito. No entanto, ela também acaba causando problemas, pois acima de uma determinada frequência, as perdas por chaveamento (como a carga e descarga do gate do MOSFET, o loop de histerese do indutor e as emissões de ondas eletromagnéticas) aumentam demasiadamente, atingindo valores impraticáveis para produtos comerciais.

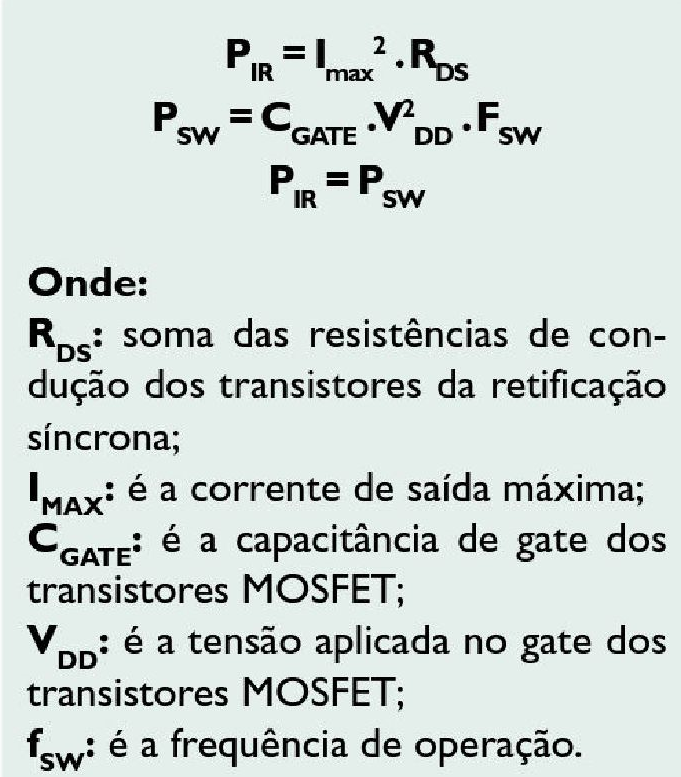

Uma boa relação sobre frequência de trabalho e ponto ótimo de operação, envolve o comparativo das perdas estáticas (ou IR) com as perdas dinâmicas (ou por chaveamento). De uma maneira simples elas podem ser exemplificadas como:

Aumentando a eficiência do POL: substituindo LDO por reguladores chaveados

Os reguladores lineares (LDO) têm dominado o mercado no que se refere a alimentação de FPGAs e MCUs de média e baixa complexidade – nos quais são necessárias correntes de até 2 A. Essa dominação deve-se ao legado das fontes lineares, da baixa necessidade de reguladores eficientes (soluções normalmente alimentadas pela rede elétrica), além de serem circuitos mais simples de se projetar – na maioria dos casos basta apenas selecionar a corrente do regulador e setar a tensão de saída. Porém, está havendo uma grande mudança nesse mercado.

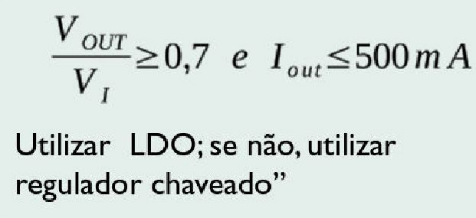

O regulador chaveado com custos cada vez mais reduzidos, package menor e ripple de saída na faixa de milivolts, além de possuir maior eficiência quando comparado ao LDO, estão fazendo com que este seja obsoletado. Outro motivador dessa mudança é a busca de muitas empresas pela redução da corrente total consumida pela equipamento (seja ligado, ou em standby) e por uma área menor de placa. Uma regra simples para descobrir onde utilizar LDO e onde utilizar conversor chaveado é dada analisando-se a relação entre tensão de saída e tensão de entrada, e a corrente de saída, como apresentado a seguir:

Numa visão macro do sistema, percebe-se que a utilização do regulador chaveado no projeto não implica apenas numa maior eficiência do POL. Mas, como o regulador chaveado irá drenar uma corrente menor nos barramentos de alimentação, o projetista pode utilizar trilhas de cobre com espessura mais fina na PCI, assim como menor área de dissipação. Além disso, pode-se reduzir também a fonte externa (reduzindo o custo), visto que a corrente drenada pelos POLs será menor.

É possível citar como outros pontos a favor dos reguladores chaveados a redução da fadiga térmica na placa (por não esquentarem tanto), a ampla gama de CIs disponíveis no mercado com tensões de entrada de 1,3 V até 76 V e corrente de saída na faixa de 75 mA até 120 A, além de inúmeros componentes com eficiência na conversão chaveada em torno de 95%!

Exemplo prático: Conversor buck (abaixador) para alimentar Core e I/O de FPGA CycloneIV, da Altera

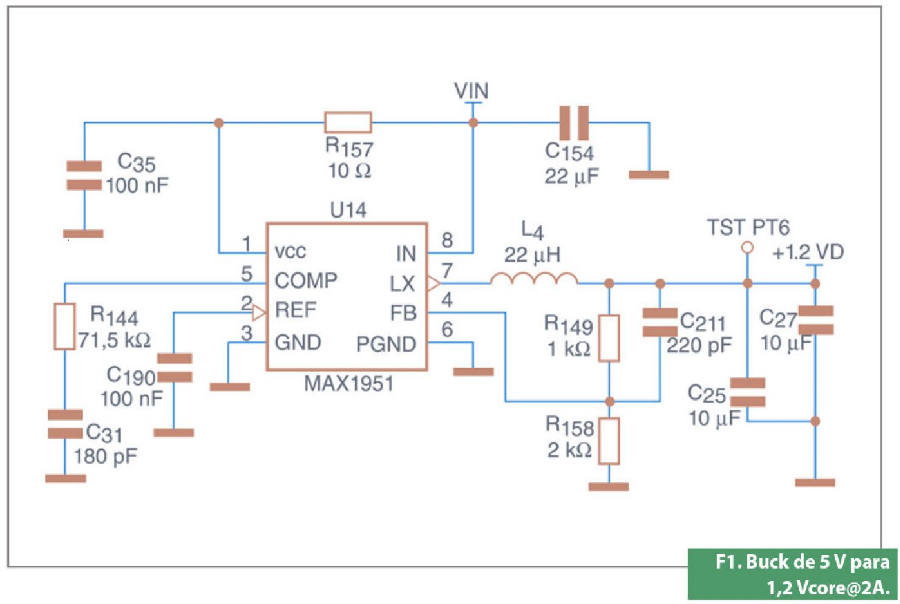

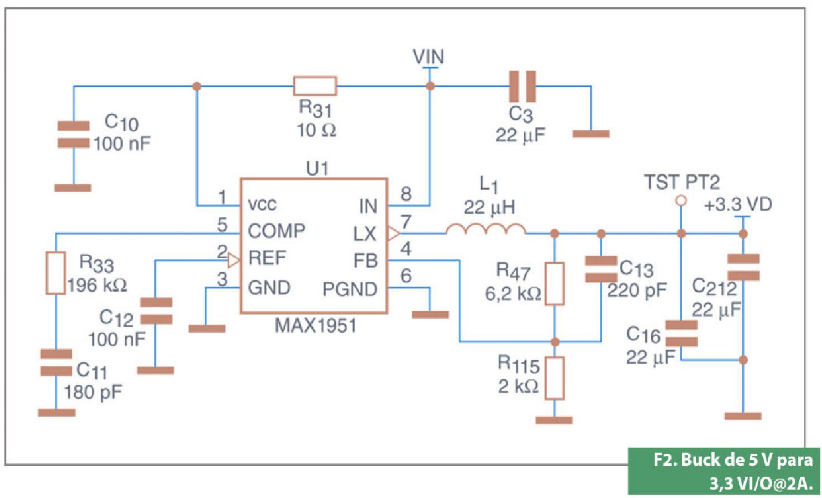

O circuito mostrado a seguir é utilizado no kit de FPGA MercuriolV® da MacnicaDHW. O mesmo consiste de dois conversores abaixadores, independentes, que geram 1,2 VDC e 3,3 VDC para alimentar, respectivamente, o Core (figura 1) e I/O (figura 2).

É utilizada uma tensão de 5 VDC - através de uma fonte externa ou USB2.0 - para alimentar os circuitos. Decidiu-se usar o MAX1951A para ambos os conversores, visto que a corrente máxima necessária em cada barramento é de aproximadamente 2 A.

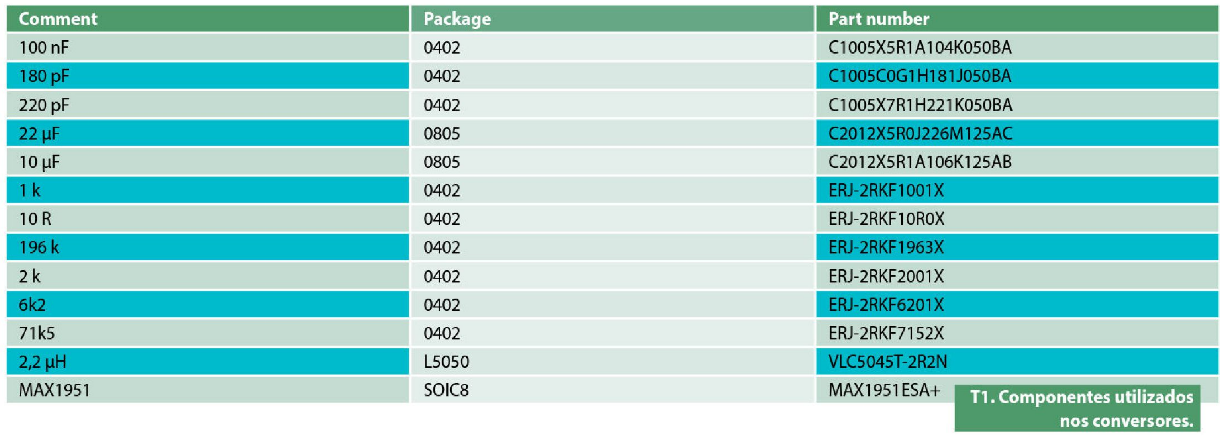

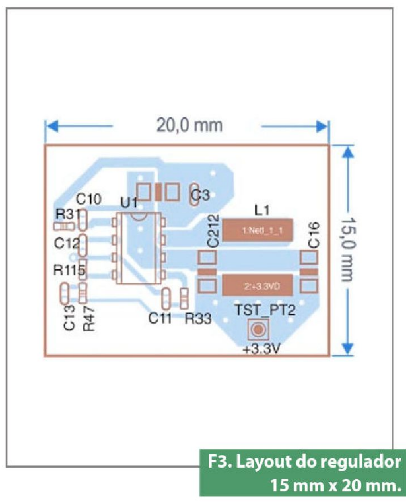

O circuito elétrico e o layout

O integrado MAX1951A é o cérebro e o coração do circuito. Ele trabalha numa frequência fixa de 1 MHz e possui internamente as chaves do lado alto e do lado baixo (retificação síncrona), o que garante reduzido espaço de placa (figura 3) aliado a alta eficiência (superior a 90% em alguns casos). O valor e tipo dos componentes passivos utilizados, vide tabela 1, foram definidos de acordo com a sugestão do fabricante Maxim Integrated, presentes na data sheet do componente.

O layout também requer atenção no seu desenvolvimento. Como sugestões estão o uso de planos e polígonos para interligar componentes que exigem correntes altas (evitando ao máximo trilhas finas); manter os capacitores de entrada e saída, indutor e CI o mais próximos possível —para reduzir loops grandes de corrente; e afastar a parte de controle (resistores de realimentação e compensação) da parte de potência — para não haver cross talk. Utilizar sempre boas práticas de layout aumenta a probabilidade de que o circuito na PCI funcione de acordo com o projeto!

Melhorando o ripple: Uso da malha de controle a seu favor

A malha de controle dos conversores tem a função de estabilizar a tensão de saída, independentemente da tensão de entrada e da corrente de saída. Para isso, é utilizado um sinal de realimentação da tensão de saída, que é comparado com um valor de referência interno para controlar as chaves de potência. Nos conversores que suportam ajuste da tensão de saída, normalmente é usado um divisor resistivo para adequar a tensão de saída à tensão de realimentação de referência. Porém, quando se utiliza apenas resistores para fazer essa adequação de tensão (exemplo: R149 e R158 da figura 1), o ripple que aparece no pino de realimentação é também um valor fracionário do ripple que está na saída. Assim, a malha de controle, por melhor que seja, não conseguirá reduzir o ripple de saída.

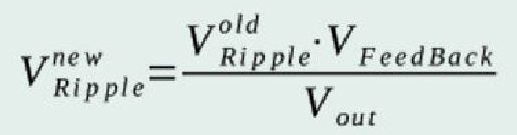

Uma maneira de resolver esse problema, é adicionar um capacitor de pequeno valor (capacitores cerâmicos na faixa de dezenas a centenas de pF são recomendados) entre o pino de realimentação e a saída do conversor (exemplo: C211 da figura 1). Ele tem a função de deixar passar apenas o valor AC ou o ripple por inteiro (e não apenas uma parte dele, caso haja um divisor resistivo somente no loop de realimentação) da saída para ser sentida através da malha de controle. Essa alteração causará uma diminuição do ripple a um valor que depende, basicamente, da tensão de realimentação do regulador (Vfb) e da tensão de saída (VOUT). Esse novo ripple pode ser calculado como:

Pode-se fazer uso desse capacitor sempre que for necessário reduzir o ripple da sua fonte (chaveada ou linear), porém, cuidado com certas malhas de controle e valores de capacitância, pois a inserção desse componente no circuito pode causar instabilidade na saída. Simulações e testes práticos são sempre bem-vindos!

Como medir o ripple?

O processo de medição do ripple de saída é simples, mas se executado de maneira incorreta, poderá introduzir erros nos resultados. Esses erros normalmente são originados pelo fio com "jacaré" de GND - entre a ponteira do osciloscópio e o circuito a ser testado - ao funcionar como antena, captando ondas eletromagnéticas presentes no ambiente e afetando o resultado. Para minimizar esses erros, ao invés de conectar o GND da ponteira através do fio com jacaré ao circuito a ser testado, utilize a ponteira de GND em forma de mola (acompanha os modelos mais novos de osciloscópio). Um outro detalhe para garantir uma medida fiel, é usar sempre os terminais do capacitor de saída e/ou entrada para conectar a ponteira do osciloscópio (sinal e GND) ao circuito a ser testado.

Capacitores cerâmicos e a sua variação com tensão DC

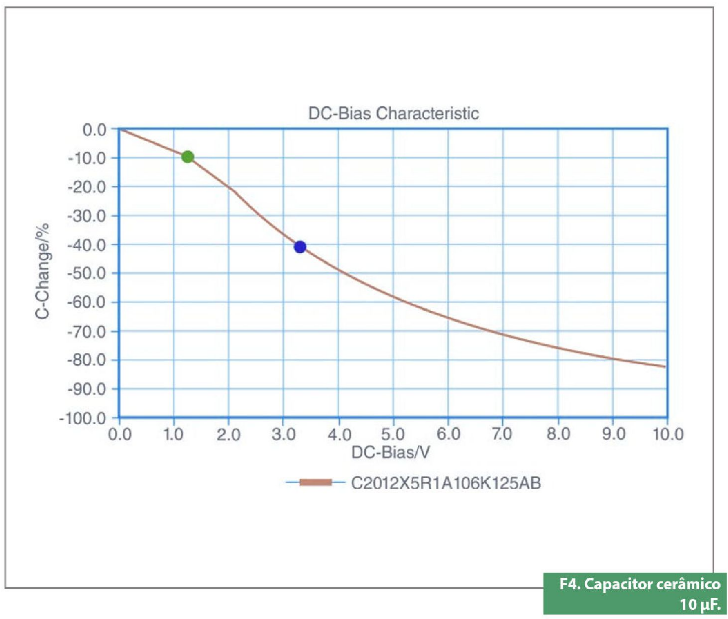

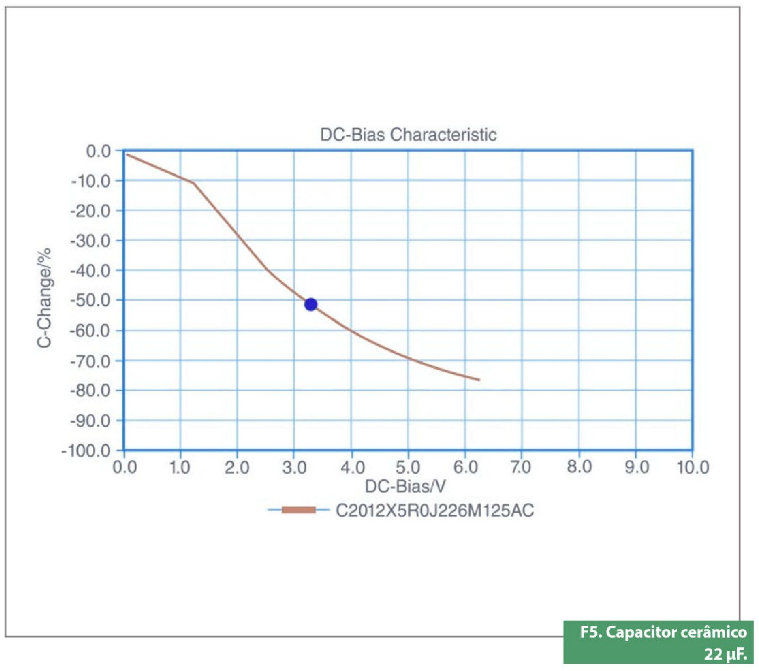

O capacitor cerâmico apresenta urna série de características que o tornam preferido para a filtragem da tensão de entrada e saída de fontes chaveadas de baixa potência. Pode-se citar como exemplos a vida útil prolongada, reduzido ESR e ESL e baixo custo. Entretanto, o capacitor cerâmico sofre grande influência negativa quando é polarizado com uma tensão DC (4) - no caso dos conversores chaveados, essa tensão DC é Vin e VOUT. As figuras 4 e 5 mostram esse comportamento para os capacitores de saída da fonte em discussão de 3,3 V e 1,2 V (22 µF e 10 µF respectivamente).

O projetista deve atentar a esse efeito e aumentar, caso necessário, o valor da capacitância de entrada e/ou saída.

Como nesse exemplo, onde o conversor de 3,3 VOUT deve ter uma capacitância de saída em torno de 20 µF de acordo com o projeto, tal fato implica em dois capacitores de 10 µF em paralelo, correto? Não, pois, devido à queda de capacitância, o valor de 10 µF em 3,3 V é 40% menor (6 µF). Com isso, a capacitância de saída seria apenas 12 µF (ponto vermelho na figura 4). Assim fez-se necessário aumentar esses capacitores para 22 µF - que em 3,3 V se torna 50% menor, ou seja, 11 µF cada um (ponto vermelho na figura 5). Para o caso da fonte de 1,2 V, a queda na capacitância é de apenas 10% (ponto verde na figura 4), o que não causa nenhum problema ao circuito.

Conclusão

Fica evidente que as empresas de desenvolvimento de hardware estão vendo os benefícios de se utilizar reguladores chaveados em seus produtos, onde uma eficiência global maior é atingida - economizando assim energia elétrica do consumidor - e custos menores de fabricação são envolvidos.

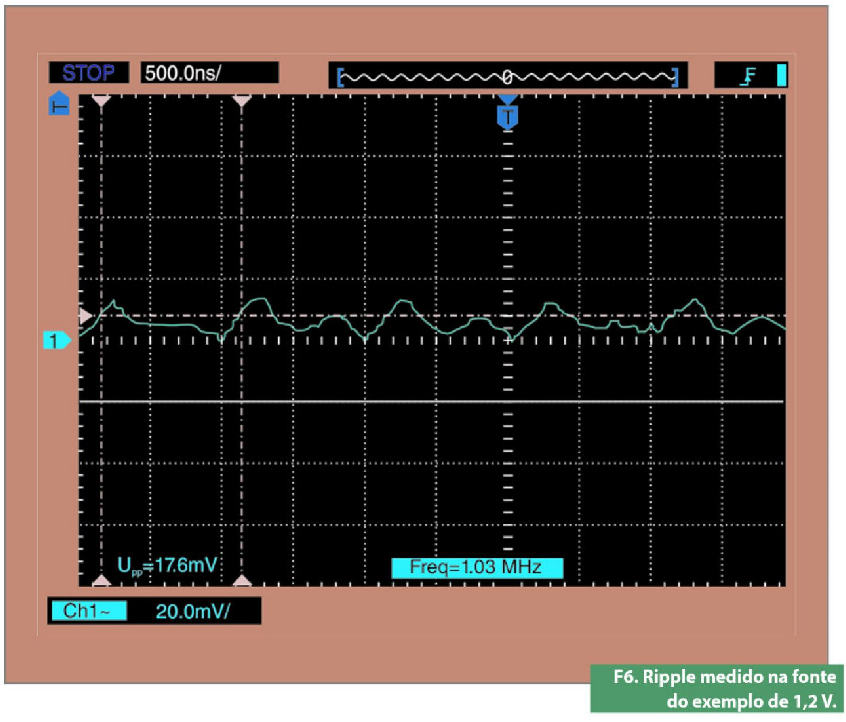

Os resultados obtidos com a implementação prática dos reguladores para o CORE e I/O do kit MercuriolV foram comprovadamente validados e atenderam todos os requisitos do projeto. Na parte do ripple de saída, chegou-se ao valor pico a pico de apenas 17,6 mV, como pode ser visto na figura 6. Um excelente resultado, visto que o CycloneIV suporta até 100 mV de oscilação na sua alimentação nesses barramentos. Caso a aplicação do leitor necessite de um ripple ainda menor, deve-se apenas adicionar uma maior capacitância na saída do conversor.

O mercado mostra que o aumento da frequência de chaveamento, na faixa de megahertz veio para ficar. Reguladores chaveados com baixo ripple de saída -comparável ao LDO e de apenas alguns milivolts - eficiência na conversão acima dos 90%, preços reduzidos e área de placa menor são apenas alguns dos motivadores dessa mudança. Inclusive já estão disponíveis reguladores que operam em frequências de até 4 MHz. Ao que tudo indica, com os avanços dos semicondutores e materiais, em alguns anos teremos fontes trabalhando na frequência de dezenas de megahertz.